|

X68000の高解像度モードの映像出力を今の液晶ディスプレイに流すと満足に映りません。本来32行あるはずのコンソール出力が下2行欠けます。理由は映像の規格が合っていなくて、液晶ディスプレイが表示可能な規格の中の近いものに無理矢理合わせて表示しているからです。しっかりと表示させるには現在では貴重品となった当時の専用CRTディスプレイをオークションなどで手に入れるか、マイコンソフト(株)が販売しているスキャンコンバータ XPC-4 を購入する必要があります(定価43,800円!)。この状況をなんとかしようと、XVIのメイン基板を改造するとともに、DDR2 SDRAMが付いたFPGA基板上にスキャンコンバータを構成し接続しました。

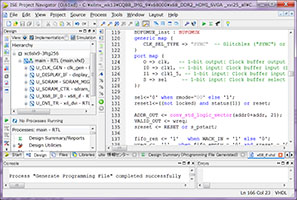

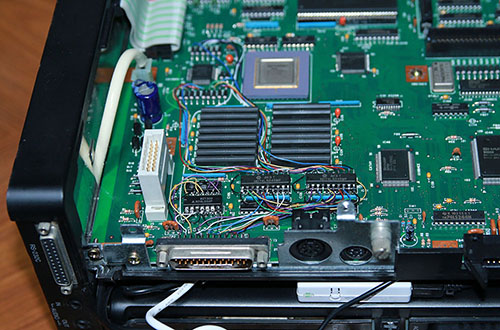

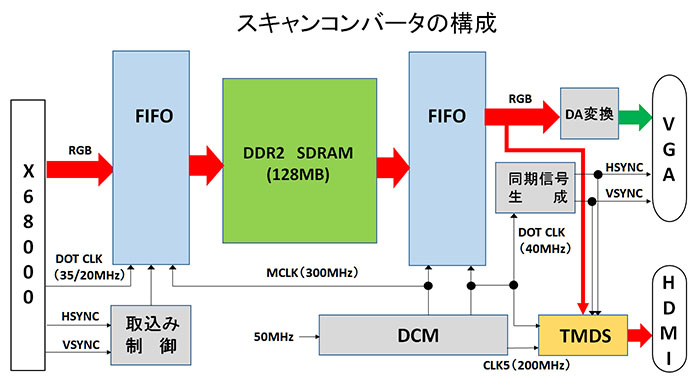

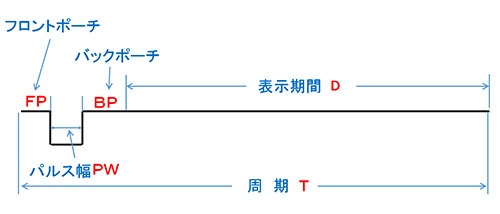

以下は回路の構成図です。  まず、X68000本体から16ビットRGBカラー信号と水平・垂直同期信号、そして、ピクセルクロック(高解像モードで約35MHz、標準モードで約20MHz)を取り出します。そして、RGBカラー信号をピクセルクロックの立ち上がりでFIFO(ファースト・イン・ファースト・アウトの略、ファイフォと呼ばれる)に入れます。FIFOの出力はシステムクロックのタイミングで DDR2 SDRAM に読み込まれ、1画面分順次記憶させます。させながら、同時に、やはり、FIFOを通して、今度はSVGAのタイミング(ピクセルクロックは40MHz)で読み出して、抵抗ラダーによるDA変換で生成したアナログのカラー信号と独自に生成した水平・垂直同期信号と合わせてVGA端子に出力させるのです。すなわち、FIFOとDDR2メモリを介することで、X68000とSVGAの信号周期の違いを吸収するわけです。また、TMDS回路によりデジタルインターフェースの「DVI」の出力に相当するシリアルRGB信号を生成し、HDMI端子に出力させるようにもしました。  左図は水平同期信号 HSYNC の波形です(垂直同期信号 VSYNC も同様)。周期Tは上の表の水平同期周波数の逆数になります。 取り込み動作は、負極正の同期信号を目印にピクセルクロックでカウンタを走らせ、(BP:バックポーチ分+SVGAとX68000の水平解像度の差の半分)の値になるまで待ってから、RGB信号のFIFOへの投入を開始していくことになります。  各種クロックの発生、取り込み制御回路やFIFO、DDR2メモリとのインタフェース、SVGAタイミング信号の生成回路やTMDS回路などは FPGA(Xilinx Spartan-6)で生成しました(左の画像参照)。 FPGAは論理回路用のパーツ、すなわち、ANDやORなど組み合わせ回路に該当するLUTとレジスタを構成するフリップフロップを多く内蔵し、プログラムコードに従って配線してくれるデバイスで、今回使用した Spartan-6 XC6SLX9 には約5000個のLUTと約1万個のフリップフロップを持っています。また、周波数や位相を自由に設定できるクロックジェネレータや少量ですがメモリも備えています。回路設計は Xilinx が無料で提供する統合開発環境ISE Web版を利用し、プログラムはVHDLで記述しました。 X68000から取り出した信号のFPGA基板への接続の中継に IMAGE IN コネクタを利用することにしました。本来はカラーイメージユニットを接続する25ピンの端子ですが、ハイビジョンがあたりまえになった現在では使うことはないでしょう(カラーイメージユニットは私も持っていますが、ヤフオクでも売れない粗大ゴミと化しています)。 ビデオコントローラ VIPS から映像用DAコンバータ(SONY CXA 1260Q-Z)に向かう16本のRGB信号とピクセルクロックを途中のフィルタの根元から取り出し、バッファICを経由して IMAGE IN コネクタに接続します。 バッファ用IC 74LS245は手持ち在庫の流用で、イメージユニットの入力バッファとして使われている74LS244の上におぶさる形で電源とGNDを半田付けして配置しました。また、やはりバッファICとして使った74LS32の向こうにあるIC(写真では見えませんが、74ALS05)のピンから水平、垂直同期信号を取り出しています。これら改造には、ソフトバンク発行の単行本「OutsideX68000」の付録、XVI回路図がたいへん役に立ちました。

ちなみに、右の写真の左端にある白いアーチ上のコネクタは映像アンプユニット接続用で、当初ここから信号がとれないか検討しました。しかし、同期信号は出ているものの、RGB信号がアナログ化されていましたので断念しました。あと、当然ながら、IMAGE IN端子にもともと繋がっていた動作に干渉する部品は全てはずしました。 IMAGE IN 端子に接続したFPGAボードには、XilinxのSpartan-6 XC6SLX9 とFPGAの初期化用フラッシュROM、128MB DDR2 SDRAM、DA変換用抵抗ラダーとVGAコネクタ、HDMIコネクタなどが載っています。技術者向けの画像処理用教材として開発されたものです。 写真左の右上から伸びているのが、ISEによって作られたプログラムファイルのダウンロードケーブルで、ケーブルを通して、FIFOやクロック発生などの回路データがパソコンからFPGAに流れます。全機能のバグがとれたらフラッシュROMに書き込んで、電源オンで即動作するようにする予定です。 写真右はXilinx提供のISE Web版によるプログラム開発画面です。プログラムは多くのVHDLファイルで構成しています。

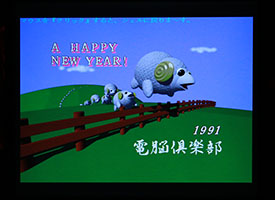

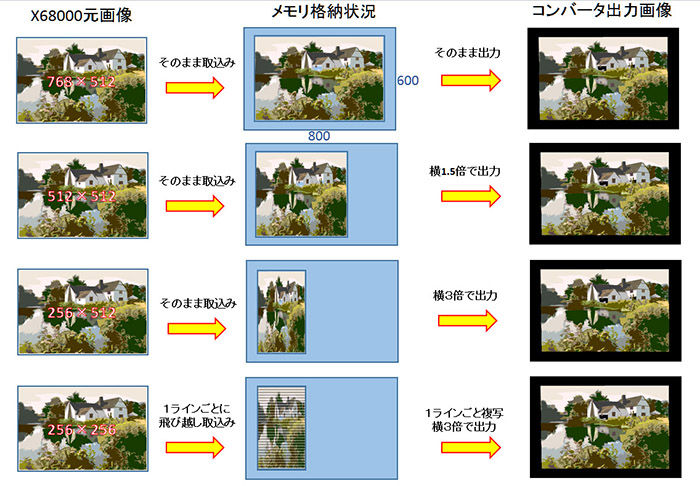

動作実験には、三菱電機のモニタ RDT171OS を使用しました。以下がそれぞれ解像度 768×512、512×512、256×512(縦二度読み)の画面をSVGA 800×600 に取り込んだ例です。解像度 768×512 では、ピクセルクロックのままで、512×512 ではピクセルクロックの1.5倍のクロックで、256×512ではピクセルクロックの3倍のクロックで取り込んでいます。これらは、現状それぞれ別のプログラムで動作しており、これらの解像度を自動判別して対応するプログラムはまだ完成していません。ネックは外部クロックを1.5倍や3倍にするFPGA内のDCM(ディジタルクロックマネージャ)で、解像度変更の際など外部クロックが途絶えた時に動作停止したり、X68000起動時に動作不安定になったりして、まとめ上げは難航しています。

なお、最近購入したCASTRADEの8インチSVGAモニタ CF-D8150AV でも表示動作を確認しております。さらに、CF-D8150AVにはHDMI入力もあり、こちらも正しく表示してくれました。誤算だったのは、うちの液晶テレビ panasonic TH-L37G2 で、これはそもそも SVGA をサポートしていないことがわかり、アナログVGA、HDMI端子とも全く映してくれませんでした。 以下は画像の各モードでのその取り込みと読み出しの様子をまとめたものです。  XPC-4など一般のスキャンコンバータは、まずPCのアナログVGA出力からAD変換をしてデジタルのカラー信号を作り、さらに、同期信号を元にPLLを利用してピクセルクロックを作り出していますが、自作したコンバータでは、これらを省き、本体から直接信号を取り出すようにしました。ピクセルクロックなどはかなりの高周波ですので、信号線の引き出しがX68000の動作を不安定にするのではないかと心配でしたが、バッファを通し、フラットケーブルの信号割り当てを考慮することでなんとか動いてくれました。 さて、製作したコンバータは現状は768×512の高解像度モードのみの使用なら、X68000の起動時から正常に動いてくれます。しかし、65536色を扱う標準解像度との切替が満足にできないと実用に耐えません。当面は、解像度ごとの別々のプログラムを1本にまとめながら、X68000の起動時はもちろん途中の解像度変更などに随時対応するようにすることが作業目標です。また、X68000には他にも解像度の種類が多くあり、それらにも出来るだけ対応していきたいと思います。今後、順次、ブログの方で報告していきます。 その後、何とか自動または手動により4つの画像モードの切り替えができるようになり、コンバータ基板を本体に実装しました。以下がその様子です。当初基板は元々のビデオアンプユニットのケース内で表向きに取り付けていましたが、FPGAの発熱で動作が不安定になってくることから、FPGAチップに放熱器を貼り付けるとともに基板を裏返し、ケースに開けた丸穴を通してファンが熱をケース外へ逃がすようにしました。IMAGE IN端子からの信号はフラットケーブルとCPU基板用コネクタを通してFPGAの端子に接続されます。基板の電源は実験段階ではACアダプタから供給しましたが、最終的には拡張BOXの裏面、コネクタの5V、GNDピンから取り出しました。

|